Analog Devices Inc. HMC7043LP7FE:一款高性能、3.2 GHz、14输出扇出缓冲器其主要特性支持JEDEC JESD204B低加性抖动: <15 fs rms(2457.6 MHz,12 kHz至20 MHz)极低噪底: -155.2 dBc/Hz (983.04 MHz)最多提供14路LVDS、LVPECL或CML型器件时钟(DCLK)CLKOUTx/CLKOUT…

Analog Devices Inc. HMC7043LP7FE:一款高性能、3.2 GHz、14输出扇出缓冲器

其主要特性

支持JEDEC JESD204B

低加性抖动: <15 fs rms(2457.6 MHz,12 kHz至20 MHz)

极低噪底: -155.2 dBc/Hz (983.04 MHz)

最多提供14路LVDS、LVPECL或CML型器件时钟(DCLK)

CLKOUTx/CLKOUTx and SCLKOUTx/SCLKOUTx 最高频率达 3200 MHz

JESD204B兼容系统参考(SYSREF)脉冲

25 ps模拟延迟和½时钟输入周期数字延迟,14个时钟输出通道各自都能对延迟进行编程

可调噪底与功耗的关系可通过SPI编程

SYSREF有效中断可简化JESD204B同步

支持确定性同步多个HMC7043器件

RFSYNC引脚或SPI控制的SYNC触发用于输出同步JESD204B

GPIO报警/状态指示用于确定系统状况

时钟输入支持高达6 GHz的频率

片内稳压器提供出色的PSRR

48引脚、7 mm × 7 mm LFCSP封装

概述

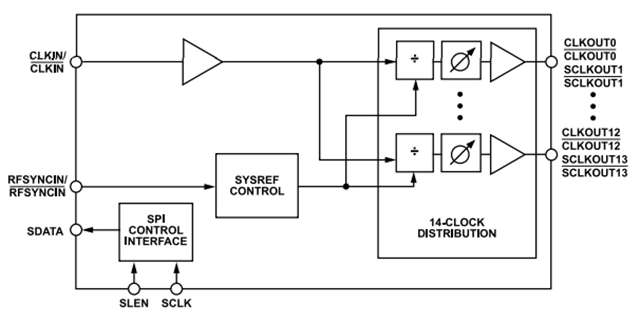

HMC7043LP7FE旨在满足多载波GSM和LTE基站设计的要求,并通过多种时钟管理和分配特性来简化基带和无线电卡时钟树的设计。

HMC7043LP7FE提供14路低噪声且可配置的输出,可以灵活地与基站收发台(BTS)系统中的许多不同器件接口,如数据转换器、本振、发射/接收模块、现场可编程门阵列(FPGA)和数字前端ASIC等。HMC7043LP7FE可生成符合JESD204B接口要求的多达7个DCLK和SYSREF时钟对。

系统设计人员可以生成更少的DCLK和SYSREF对,并针对独立的相位和频率配置其余的输出信号路径。 DCLK和SYSREF时钟输出均可配置为支持CML、LVDS、LVPECL和LVCMOS等不同的信号标准,不同的偏置条件则可调整变化的板插入损耗。

HMC7043LP7FE独特的特性之一是对14个通道分别进行独立灵活的相位管理。所有14个通道均支持频率和相位调整。 这些输出还可针对50 Ω或100 Ω内部和外部端接选项进行编程。

HMC7043LP7FE器件具有RF SYNC功能,支持确定性同步多个HMC7043器件,即确保所有时钟输出从同一时钟沿开始。 可通过改写嵌套式HMC7043LP7FE或SYSREF控制单元/分频器,然后重新启动具有新相位的输出分频器来实现。

HMC7043LP7FE采用48引脚、7 mm × 7 mm LFCSP封装,且裸露焊盘接地。

HMC7043LP7FE具备以下关键参数:

PLL:是

输入:时钟

输出:CML,LVDS,LVPECL

电路数:1

比率 - 输入:输出:1:14

差分 - 输入:输出:是/是

频率 - 最大值:3.2GHz

分频器/倍频器:是/无

电压 - 供电:3.135V ~ 3.465V

工作温度:-40°C ~ 85°C

安装类型:表面贴装型

封装/外壳:48-LFCSP

此外,HMC7043LP7FE时钟缓冲器广泛应用于多种应用场景,主要包括:

JESD204B时钟产生

蜂窝基础设施(多载波GSM、LTE、W-CDMA)

数据转换器时钟

相控阵参考分配

微波基带卡

如需采购HMC7043LP7FE时钟缓冲器,欢迎访问明佳达电子官网(www.hkmjd.com)查询详情。

电话咨询:86-755-83294757

企业QQ:1668527835/ 2850151598/ 2850151584/ 2850151585

服务时间:9:00-18:00

联系邮箱:chen13410018555@163.com/sales@hkmjd.com

公司地址:广东省深圳市福田区振中路新亚洲国利大厦1239-1241室

CopyRight©2022 版权归明佳达电子公司所有 粤ICP备05062024号-12

官方二维码

友情链接: